# 22V, 15A, Synchronous Buck Regulator with 2-Bit VID

December 20, 2022

# **Description**

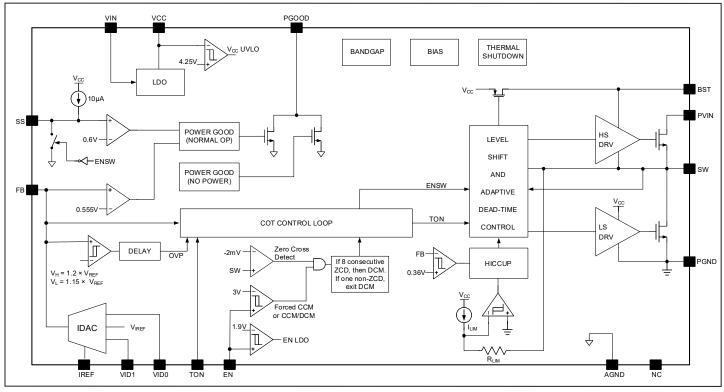

The MxL76125 device is a synchronous step-down regulator combining the controller, driver, bootstrap diode, and MOSFETs in a single package for point-of-load supplies. The MxL76125 device is rated for 15A load. A wide input voltage range from 5V to 22V allows for single supply operation from industry standard 5V, 12V, and 20V rails.

With a proprietary emulated current mode constant on-time (COT) control scheme, the MxL76125 device provides extremely fast line and load transient response using ceramic output capacitors. The controller does not require any external loop compensation, which simplifies the circuit implementation and reduces the overall component count. It also provides 0.1% load and 0.1% line regulation, and maintains constant switching frequency. A selectable power saving mode enables operation in discontinuous conduction mode (DCM) at light loads, thereby significantly increasing the converter efficiency.

The MxL76125 has a 2-bit VID, meeting the core rail requirements of MaxLinear's MxL317xx Wi-Fi 7 SoCs. The VID allows the Wi-Fi 7 SoC to optimize performance while minimizing power consumption in both active and idle states by dynamically changing the output voltage of the MxL76125.

A host of protection features, including overcurrent, over temperature, overvoltage, short-circuit, and UVLO, helps achieve safe operation under abnormal operating conditions.

The MxL76125 device is available in a RoHS compliant, green/halogen-free space-saving 4mm x 5mm QFN package.

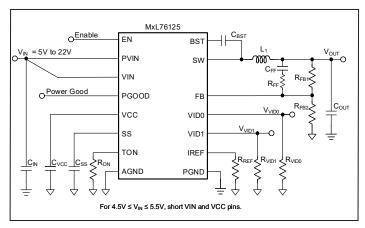

Figure 1. MxL76125 Typical Application Diagram

#### **FEATURES**

- 15A step-down regulator

- □ Low V<sub>IN</sub> operation from 4.5V to 5.5V

- Wide single input voltage from 5V to 22V

- V<sub>IN</sub> operation from 1V to 22V with external 5V bias

- □ ≥0.6V adjustable output voltage

- 2-bit VID for MaxLinear Wi-Fi 7 SoCs

- Adjustable VID resolution through R<sub>REF</sub>

- Proprietary constant on-time control

- □ No loop compensation required

- Stable operation with ceramic output capacitors

- □ Programmable on-time ≥ 40ns

- □ Constant 200kHz-1.25MHz frequency

- □ Selectable forced CCM or CCM/DCM operation

- Output over-voltage, over-current and over-temperature protections

- Power-good flag with low impedance when power is removed

- Precision enable

- Programmable soft-start time

- 4mm x 5mm QFN package

#### **APPLICATIONS**

- MaxLinear Wi-Fi SoC core rail

- Puma® and AnyWAN® based CPE

- Servers

- Distributed power architecture

- FPGA, DSP and processor supplies

- Base stations, switches/routers

For more details about the ordering information, see "Ordering Information" on page 20.

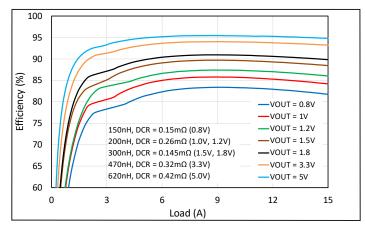

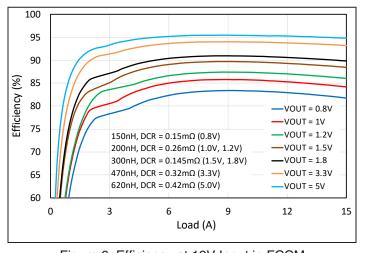

Figure 2. Efficiency at  $V_{IN}$ =12V and  $F_{SW}$  = 1MHz

# **Absolute Maximum Ratings**

These are stress ratings only and functional operation of the device at these ratings is not implied. Stresses beyond these ratings may cause permanent damage to the device. Exposure to any absolute maximum rating condition for extended periods may affect device reliability and lifetime.

| PV <sub>IN</sub> , V <sub>IN</sub> | From -0.3V to 25V                    |

|------------------------------------|--------------------------------------|

| V <sub>CC</sub>                    | From -0.3V to 6.0V                   |

| BST                                | From -0.3V to 31V <sup>(1)</sup>     |

| BST-SW                             | From -0.3V to 6V                     |

| SW                                 | From -1V to 25V <sup>(1)(2)</sup>    |

| All other pins                     | From -0.3V to V <sub>CC</sub> + 0.3V |

| Storage temperature                | From -65°C to 150°C                  |

| Power dissipation                  | Internally limited                   |

| Lead temperature (soldering, 10    | second)300°C                         |

| ESD rating (Human body model-      | -HBM)±2kV                            |

| ESD rating (Charged device mod     | del-CDM)±500V                        |

|                                    |                                      |

# **Operating Conditions**

These are the conditions under which the device is intended to function.

| PV <sub>IN</sub> From 1V to 22V                                 |

|-----------------------------------------------------------------|

| V <sub>IN</sub> From 4.5V to 22V                                |

| V <sub>CC</sub> From 4.5V to 5.5V                               |

| SW, From -1V to 22V <sup>(2)</sup>                              |

| PGOOD, TON, SS, ENFrom -0.3V to 5.5V                            |

| Switching frequencyFrom 200kHz to 1.25MHz <sup>(3)</sup>        |

| Junction temperature range (T <sub>J</sub> )From -40°C to 125°C |

| Power dissipation max at T <sub>A</sub> = 70°C2.46W             |

| Package thermal resistance, junction to ambient, $\theta_{JA}$  |

| Junction-to-bottom thermal                                      |

| characteristic parameter, $\psi_{JB}$                           |

- 1. No external voltage applied.

- 2. SW pin can go  $\pm 5\text{V}$  away with respect to the steady state value during switch transition, for 50ns.

- 3. Typical.

- 4. Thermal simulation data.

#### **Electrical Characteristics**

Specifications are for operating junction temperature of  $T_J = 25^{\circ}C$  only; limits applying over the full operating junction temperature range are denoted by a  $\bullet$ . Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated, PVIN is not connected,  $V_{IN} = 12V$ , SW = AGND = PGND = 0V,  $C_{VCC} = 4.7uF$ .

| Symbol                       | Parameter                                     | Conditions                                                   | • | Min  | Тур | Max | Units |

|------------------------------|-----------------------------------------------|--------------------------------------------------------------|---|------|-----|-----|-------|

| Power Supp                   | ly Characteristics                            |                                                              |   |      |     |     |       |

| V                            | Input voltage range                           | V <sub>CC</sub> regulating                                   |   | 5    | 12  | 22  | V     |

| V <sub>IN</sub>              | Input voltage range                           | V <sub>CC</sub> tied to V <sub>IN</sub>                      |   | 4.5  | 5.0 | 5.5 | V     |

| I <sub>VIN</sub>             | V <sub>IN</sub> supply current                | Not switching, V <sub>IN</sub> = 12V, V <sub>FB</sub> = 0.7V | • | -    | 0.8 | 1   | mA    |

| lvcc                         | V <sub>CC</sub> quiescent current             | Not switching, $V_{CC} = V_{IN} = 5V$ , $V_{FB} = 0.7V$      | • | -    | 0.8 | 1   | mA    |

| I <sub>VIN</sub>             | V <sub>IN</sub> supply current                | $F_{SW} = 1MHz$ , $V_{IN} = PV_{IN} = 12V$                   | • | 18.9 | 20  | 21  | mA    |

| I <sub>OFF</sub>             | Shutdown current                              | Enable = 0V, PV <sub>IN</sub> = V <sub>IN</sub> = 12V        |   | -    | -   | 1   | μΑ    |

| Enable, FCC                  | Enable, FCCM and CCM/DCM Modes of Operation   |                                                              |   |      |     |     |       |

| V <sub>IH_EN</sub><br>_FCCM  | EN pin rising threshold for FCCM operation    | -                                                            | • | 1.8  | 1.9 | 2.0 | V     |

| V <sub>EN_HYS_</sub><br>FCCM | EN pin hysteresis for FCCM operation          | -                                                            |   | -    | 50  | -   | mV    |

| VIH_EN _DCM                  | EN pin rising threshold for CCM/DCM operation | -                                                            | • | 2.9  | 3   | 3.1 | V     |

| VEN_HYS_<br>DCM              | EN pin hysteresis for CCM/DCM operation       | -                                                            |   | -    | 100 | -   | mV    |

# **Electrical Characteristics (Continued)**

Specifications are for operating junction temperature of  $T_J = 25^{\circ}C$  only; limits applying over the full operating junction temperature range are denoted by a  $\bullet$ . Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated, PVIN is not connected,  $V_{IN} = 12V$ , SW = AGND = PGND = 0V,  $C_{VCC} = 4.7uF$ .

| Symbol                   | Parameter                                         | Conditions                                                                             | • | Min   | Тур   | Max   | Units |

|--------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|---|-------|-------|-------|-------|

| VID Levels               |                                                   |                                                                                        |   |       |       |       |       |

| V <sub>IREF</sub>        | IREF pin voltage                                  | -                                                                                      |   | 544   | 556   | 569   | mV    |

|                          |                                                   | VID1 = 0b0, VID0 = 0b0, R <sub>REF</sub> = 56.2kΩ ±1%                                  | • | -10   | 0     | 10    | nA    |

|                          |                                                   | VID1 = 0b0, VID0 = 0b1, R <sub>REF</sub> = 56.2kΩ ±1%                                  | • | -10.1 | -9.91 | -9.72 | μΑ    |

| I <sub>FB</sub>          | FB pin sourcing current                           | VID1 = 0b1, VID0 = 0b0, $R_{REF} = 56.2$ kΩ ±1%                                        |   | 9.72  | 9.91  | 10.1  | μΑ    |

|                          |                                                   | VID1 = 0b1, VID0 = 0b1, R <sub>REF</sub> = 56.2kΩ ±1%                                  | • | 19.44 | 19.82 | 20.2  | μΑ    |

| -                        | VID logic low threshold                           | -                                                                                      | • | -     | -     | 0.4   | V     |

| -                        | VID logic high threshold                          | -                                                                                      | • | 2.4   | -     | -     | V     |

| Undervoltage             | e Lock-Out UVLO                                   |                                                                                        | , | '     | '     |       | '     |

| -                        | V <sub>CC</sub> UVLO start threshold, rising edge | -                                                                                      | • | 4.00  | 4.25  | 4.40  | V     |

| -                        | V <sub>CC</sub> UVLO hysteresis                   | -                                                                                      | • | 100   | 170   | -     | mV    |

| Feedback Ro              | eference Voltage                                  |                                                                                        |   |       |       |       |       |

|                          | Feedback reference voltage                        | V <sub>IN</sub> = 5V-22V, V <sub>CC</sub> regulating                                   |   | 0.597 | 0.600 | 0.603 | V     |

| $V_{FB}$                 |                                                   | $V_{IN} = 4.5V-5.5V$ , $V_{CC}$ tied to $V_{IN}$                                       |   | 0.596 | 0.600 | 0.604 | V     |

|                          |                                                   | $V_{IN}$ = 5V-22V, $V_{CC}$ regulating $V_{IN}$ = 4.5V-5.5V, $V_{CC}$ tied to $V_{IN}$ | • | 0.594 | 0.600 | 0.606 | V     |

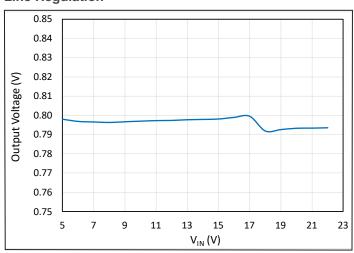

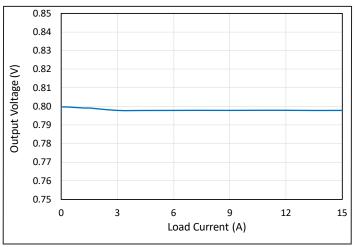

| -                        | DC load regulation                                | CCM operation, closed loop,                                                            |   | -     | ±0.1  | -     | %     |

| -                        | DC line regulation                                | applies to any C <sub>OUT</sub>                                                        |   | -     | ±0.1  | -     | %     |

| Programmab               | ole Constant On-Time                              |                                                                                        |   |       |       |       |       |

| -                        | On-time 1                                         | R <sub>ON</sub> = 1.82kΩ, PV <sub>IN</sub> = 12V                                       |   | -     | 78    | -     | ns    |

| -                        | f corresponding to on-time 1                      | V <sub>OUT</sub> = 0.8V, Load = 11.5A, Efficiency = 81%                                |   | -     | 1     | -     | MHz   |

| -                        | On-time 2                                         | $R_{ON} = 8.66k\Omega, PV_{IN} = 12V$                                                  |   | -     | 275   | -     | ns    |

| -                        | f corresponding to on-time 2                      | V <sub>OUT</sub> = 3.3V, Load = 8.4A, Efficiency = 94%                                 |   | -     | 1     | -     | MHz   |

| Minimum Off              | f-Time                                            |                                                                                        |   |       |       |       |       |

| -                        | Minimum off-time                                  | -                                                                                      | • | -     | 250   | 350   | ns    |

| Soft-Start               |                                                   |                                                                                        |   |       |       |       |       |

| I <sub>SS_CHARGE</sub>   | Charge current                                    | -                                                                                      | • | -14   | -10   | -6    | μΑ    |

| ISS_DISCHARGE            | Discharge current                                 | Fault present                                                                          | • | 1     | 3     | -     | mA    |

| V <sub>CC</sub> Linear F | Regulator                                         |                                                                                        |   |       |       |       |       |

|                          |                                                   | V 6V 20V I 0.20m A                                                                     |   | 4.0   | F 0   | F 0   | V     |

| V <sub>CC</sub>          | Output voltage                                    | $V_{IN} = 6V-22V, I_{LOAD} = 0-30mA$                                                   | • | 4.8   | 5.0   | 5.2   | V     |

# **Electrical Characteristics (Continued)**

Specifications are for operating junction temperature of  $T_J = 25^{\circ}C$  only; limits applying over the full operating junction temperature range are denoted by a  $\bullet$ . Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated, PVIN is not connected,  $V_{IN} = 12V$ , SW = AGND = PGND = 0V,  $C_{VCC} = 4.7uF$ .

| Symbol        | Parameter                                               | Conditions                                                             | • | Min | Тур  | Max | Units |

|---------------|---------------------------------------------------------|------------------------------------------------------------------------|---|-----|------|-----|-------|

| Power Good    | Power Good Output                                       |                                                                        |   |     |      |     |       |

| -             | Power good threshold                                    | -                                                                      |   | -10 | -7.5 | -5  | %     |

| -             | Power good hysteresis                                   | -                                                                      |   | -   | 1    | 4   | %     |

| -             | Power good de-assertion voltage                         | Maximum ISINK = 1mA                                                    |   | -   | -    | 0.2 | V     |

| -             | Power good, unpowered (V <sub>IN</sub> = 0)             | ISINK = 1mA                                                            |   | -   | -    | 0.5 | V     |

| -             | Power good assertion delay,<br>FB rising                | -                                                                      |   | -   | 2    | -   | ms    |

| -             | Power good de-assertion delay,<br>FB falling            | -                                                                      |   | -   | 65   | -   | μs    |

| OVP Detect    |                                                         |                                                                        |   |     |      |     |       |

| -             | OVP trip high threshold                                 | V <sub>FB</sub> rising. Specified as % of V <sub>REF</sub>             | • | 115 | 120  | 125 | %     |

| -             | OVP trip low threshold                                  | V <sub>FB</sub> falling. Specified as % of V <sub>REF</sub>            | • | -   | 115  | -   | %     |

| -             | OVP comparator delay                                    | V <sub>FB</sub> rising                                                 | • | 0.5 | 1    | 3.5 | μs    |

| -             | Delay to turn off power stage from an overvoltage event | V <sub>FB</sub> rising                                                 | • | -   | -    | 3.5 | μs    |

| Protection: 0 | OCP, OTP, Short-Circuit                                 |                                                                        |   |     |      |     |       |

| -             | Hiccup timeout                                          | -                                                                      | • | 102 | 105  | 107 | ms    |

| -             | OCP threshold (Valley current)                          | -                                                                      |   | -   | 20   | -   | Α     |

| -             | Current limit blanking                                  | -                                                                      |   | -   | 100  | -   | ns    |

| -             | Thermal shutdown threshold                              | Rising temperature                                                     |   | -   | 138  | -   | °C    |

| -             | Thermal hysteresis                                      | -                                                                      |   | -   | 15   | -   | °C    |

| -             | Feedback pin short-circuit threshold                    | % of V <sub>REF</sub> Short-circuit is active     Soft-start completed | • | 50  | 60   | 70  | %     |

| MxL76125 (    | Output Power Stage                                      |                                                                        |   |     |      |     |       |

| -             | High-side MOSFET R <sub>DS(ON)</sub>                    | I <sub>DS</sub> = 2A                                                   |   | -   | 9    | -   | mΩ    |

| -             | Low-side MOSFET R <sub>DS(ON)</sub>                     | I <sub>DS</sub> = 2A                                                   |   | -   | 3.6  | -   | mΩ    |

| -             | Rated output current                                    |                                                                        | • | 15  | -    | -   | А     |

| Thermal Re    | sistance                                                |                                                                        |   |     |      |     |       |

| -             | Junction to package top                                 | -                                                                      | • | -   | 37.4 | -   | °C/W  |

| -             | Junction to package bottom                              | -                                                                      | • | -   | 5.6  | -   | °C/W  |

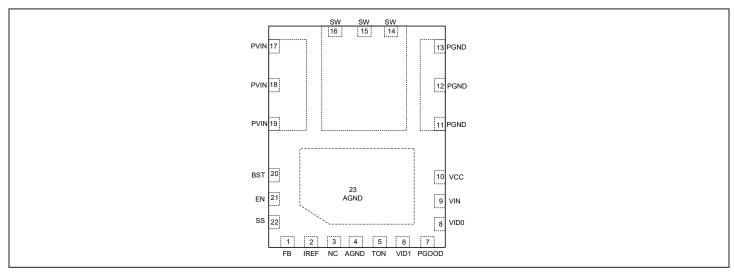

# **Pin Configuration**

Figure 3. MxL76125 Pin Configuration (Top View)

# **Pin Functions**

| Pin Number | Pin Name | Туре               | Description                                                                                                                                     |

|------------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB       | Analog             | Input to the feedback comparator. The reference is fixed at 600mV.                                                                              |

| 2          | IREF     | Analog             | VID reference current setting pin. Connect a 56.2kΩ resistor to AGND.                                                                           |

| 3          | NC       | None               | Not connected.                                                                                                                                  |

| 4          | AGND     | Analog             | Signal ground for control circuitry. Internally connected to AGND pad.                                                                          |

| 5          | TON      | Analog             | Constant on-time programming pin. Connect a resistor to AGND.                                                                                   |

| 6          | VID1     | Input              | MSB of the 2-bit VID reference. Connect a pulldown resistor, R <sub>VID1</sub> to AGND. It should not be floating.                              |

| 7          | PGOOD    | Output, open drain | Power-good output. Open drain to AGND. Low Z when IC unpowered.                                                                                 |

| 8          | VID0     | Input              | LSB of the 2-bit VID reference. Connect a pulldown resistor, R <sub>VID0</sub> to AGND. It should not be floating.                              |

| 9          | VIN      | Analog             | Supply input for the regulator's LDO. Connect to PVIN at CIN.                                                                                   |

| 10         | VCC      | Analog             | The output of regulators LDO. It requires a 4.7 $\mu$ F VCC bypass capacitor. For V <sub>IN</sub> = 5V, VCC should be tied to VIN.              |

| 11, 12, 13 | PGND     | Power              | Ground of the power stage. Internally connected to source of the low-side MOSFET.                                                               |

| 14, 15, 16 | sw       | Power              | Switch node. Internally it connects source of the high-side MOSFET to drain of the low-side MOSFET.                                             |

| 17, 18, 19 | PVIN     | Power              | Input voltage for power stage. Internally connected to drain of the high-side MOSFET.                                                           |

| 20         | BST      | Analog             | High-side driver power supply pin. Connect a 1uF boot-strap capacitor between BST and SW pins.                                                  |

| 21         | EN       | Input              | Precision enable input. The voltage level decides FCCM and CCM/DCM modes of operation. For details, see "Electrical Characteristics" on page 2. |

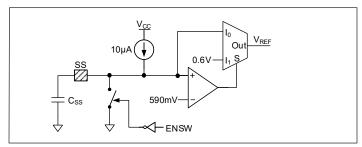

| 22         | SS       | Analog             | Soft start pin. Connect an external capacitor between SS and AGND to program the softstart rate based on a 10µA internal source current.        |

| 23         | AGND PAD | Analog             | Signal ground for control circuitry.                                                                                                            |

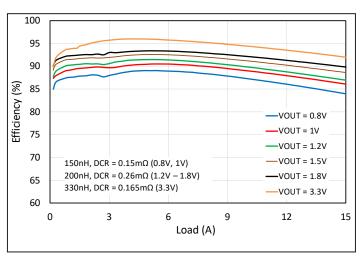

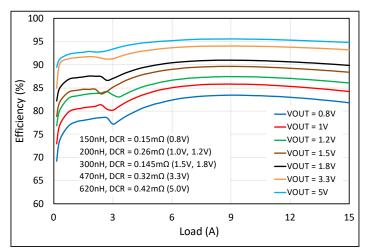

# **Typical Performance Characteristics**

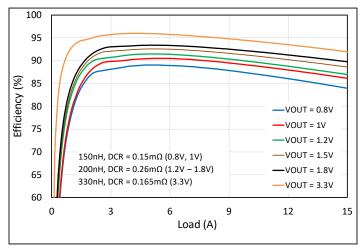

Unless otherwise specified:  $V_{IN}=12V,~V_{OUT}=0.8V,~F_{SW}=1$ MHz, VCC=5.0V internally generated,  $C_{OUT}=265\mu F,~L=150$ nH (DCR =  $0.15m\Omega$ ),  $C_{FF}=470$ pF,  $R_{FF}=0\Omega,~R_{FB1}=4.99$ k $\Omega,~R_{FB2}=15$ k $\Omega,~FCCM$  mode of operation,  $T_{AMBIENT}=25$ °C, and no airflow. Efficiency data includes inductor losses.

# **Efficiency**

Figure 4. Efficiency at 5V Input in FCCM (VIN and VCC are shorted)

Figure 6. Efficiency at 12V Input in FCCM

Figure 5. Efficiency at 5V Input in DCM (VIN and VCC are shorted)

Figure 7. Efficiency at 12V Input in DCM

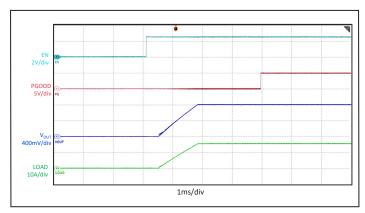

# **Startup Sequence**

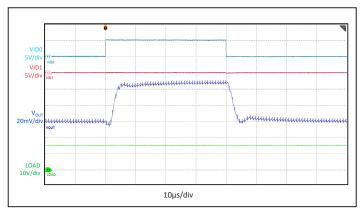

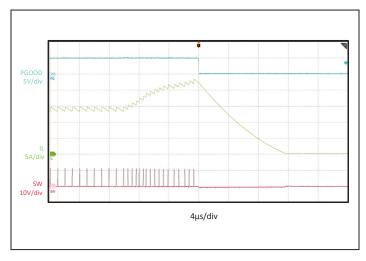

Figure 8. Power-up: I<sub>OUT</sub> = 15A at 0.8V

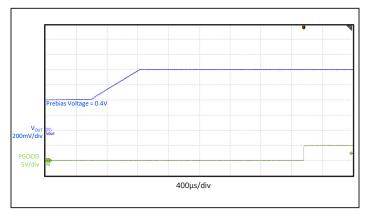

Figure 9. Startup with Prebias Voltage of 400mV:  $I_{OUT} = 20mA$

# **Shutdown Sequence**

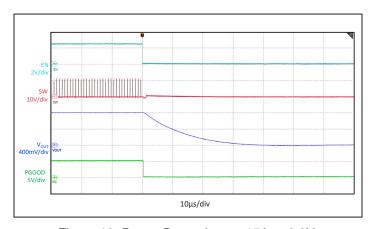

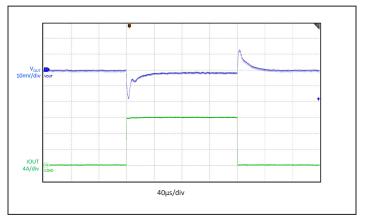

Figure 10. Power Down: I<sub>OUT</sub> = 15A at 0.8V

# Steady State V<sub>OUT</sub> Ripple

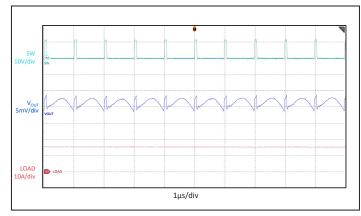

Figure 11. Steady State  $V_{OUT}$  Ripple:  $I_{OUT} = 15A$ ,  $V_{OUT} = 0.8V$

# DVS

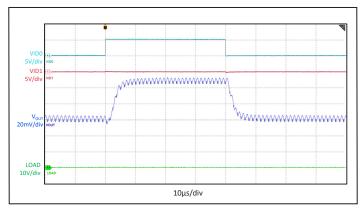

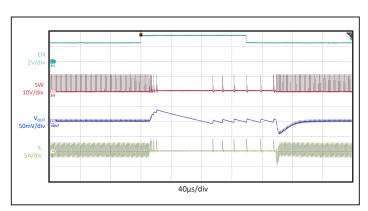

Figure 12. DVS:  $V_{OUT}$  = 0.8V to 0.85V and Back;  $I_{OUT}$  = 0A; Settling Time = ~4 $\mu$ s

Figure 13. DVS:  $V_{OUT} = 0.8V$  to 0.85V and Back;  $I_{OUT} = 15A$ ; Settling Time = ~4 $\mu$ s

#### **Load Transients**

Figure 14. Load Transient from 1.5A to 13.5A and Back in FCCM ( $C_{OUT}=350\mu F)$

# ZOmV/div voor IOUT 4A/div voor 20µs/div

Figure 15. Load Transient from 1.5A to 13.5A and Back in DCM ( $C_{OUT} = 350 \mu F$ )

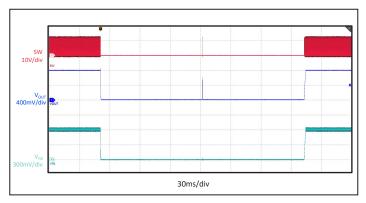

#### **FCCM-DCM Transition**

Figure 16. FCCM Mode to DCM Mode and Back:  $I_{OUT} = 100 mA$

# **Short Circuit Recovery**

FB pin momentary shorted with AGND

Figure 17. Short Circuit Hiccup and Recovery

### **Over Current Protection**

Figure 18. Shutdown during Over Current

# **Line Regulation**

Figure 19. Line Regulation

# **Load Regulation**

Figure 20. Load Regulation

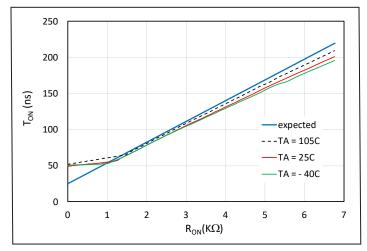

# T<sub>ON</sub> vs R<sub>ON</sub> Correlation

Figure 21. T<sub>ON</sub> vs R<sub>ON</sub> Correlation: I<sub>OUT</sub> = 15A

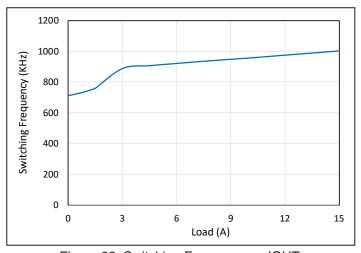

# Frequency vs I<sub>OUT</sub>

Figure 22. Switching Frequency vs IOUT

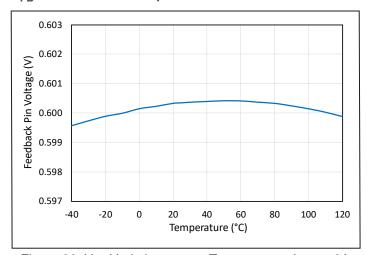

# **V<sub>FB</sub> Variation with Temperature**

Figure 23. V<sub>FB</sub> Variation across Temperature: I<sub>OUT</sub> = 0A

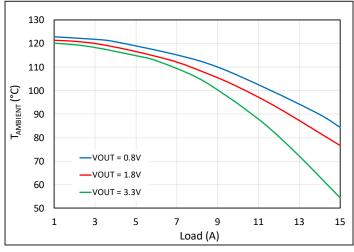

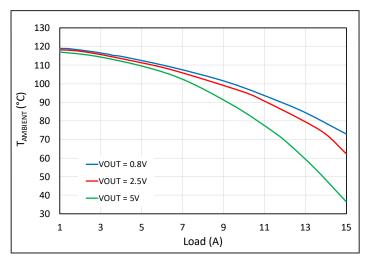

# **Thermal Derating Curves**

Figure 24. Maximum Ambient Temperature vs. Load Current, V<sub>IN</sub> = 5V

Figure 25. Maximum Ambient Temperature vs. Load Current,  $V_{IN} = 12V$

# **Functional Block Diagram**

Figure 26. MxL76125 Functional Block Diagram

# **Applications Information**

# **Detailed Operation**

The MxL76125 device is a 15A synchronous step-down switching voltage regulator with a 2-bit VID. MOSFETs, controller, driver, and bootstrap diode are combined in a single package for point-of-load supplies. The output voltage and VID step size are adjustable by external components. The 2-bit VID functionality is targeted to meet core rail requirements of MaxLinear's MxL317xx Wi-Fi 7 SoCs. The VID enables the Wi-Fi SoC to dynamically change the output voltage to switch between active and power saving idle states.

The MxL76125 uses a proprietary emulated current-mode constant on-time (COT) control scheme. The on-time ( $T_{ON}$ ) is programmable by an external resistor ( $R_{ON}$ ) and is inversely proportional to  $V_{IN}$ . The latter feature offers nearly constant switching frequency over a large  $V_{IN}$  range. The emulated current-mode control allows you to use ceramic capacitors (low ESR) in the output filter.

The MxL76125 can operate in both, forced continuous conduction mode (FCCM) for low switching ripple and power saving discontinuous conduction mode (DCM) at light loads. The mode is set by EN voltage levels, as described in the "Enable Input" section.

# **Enable Input**

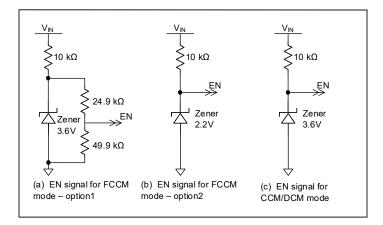

The enable input (EN) is a high impedance input pin and accepts a tri-level signal. The voltage levels and corresponding functionalities are as follows:

- EN < 1.7V: The MxL76125 is off.

- 2.0V≤ EN < 2.8V: The MxL76125 runs in FCCM mode at all loads.

- EN ≥ 3.1V: The MxL76125 runs in DCM at light loads.

#### **FCCM Mode**

This mode is active when the EN pin voltage is between 2.0V and 2.8V. The pin voltage can be controlled by an external signal. Alternatively, it can be derived from  $V_{IN}$ . For a well-regulated supply  $(V_{IN})$ , a resistor divider can be used. In order to account for any small variations in  $V_{IN}$ , MaxLinear recommends you to set the EN voltage to 2.5V. For wide range of  $V_{IN}$ , circuits as shown in Figure 27(a) and 27(b) can be used.

#### **DCM/CCM Mode**

To enable DCM operation at light loads, ensure that the EN pin voltage is from 3.1V to 5.5V. Like the FCCM mode, the voltage can be controlled by an external signal or can be derived from  $V_{IN}$  by using a resistor and a Zener diode, as shown in Figure 27(c). This is valid for the entire range of  $V_{IN}$ . However, for a well-regulated  $V_{IN}$ , you can use a resistor divider. To account for any small variations in  $V_{IN}$ , MaxLinear recommends you to set the EN voltage to 4V.

Figure 27. Options to Select FCCM or CCM/DCM Mode using  $V_{IN}$

# **Programming the Soft Start Time**

Figure 28 on page 12 shows a block diagram of the soft-start functionality. During soft start, the feedback reference voltage,  $V_{REF}$ , is tied to the SS pin. This pin forces  $10\mu A$  current into  $C_{SS}$ , between the pin and AGND.  $V_{REF}$  is the same as  $V_{CSS}$  and increases linearly as follows:

$$\frac{dV_{REF}}{dt} = \frac{dV_{CSS}}{dt} = \frac{10\mu A}{C_{SS}}; \quad V_{CSS} = V_{REF} \le 590 \text{mV} \quad (1)$$

When the  $V_{CSS}$  voltage reaches 590mV,  $V_{REF}$  connection shifts from the SS pin to 0.6V, and soft start completes. For a given soft start time ( $t_{SS}$ ), the required value of  $C_{SS}$  is as follows:

$$C_{SS} = t_{SS} \times \frac{10 \mu A}{590 \text{mV}}$$

(2)

239DSR01

# **Applications Information (Continued)**

Figure 28. Start Soft Block Diagram

Soft start occurs in the following conditions:

- EN toggles from low to high.

- EN is high and VCC rises above the UVLO threshold.

- A fault occurs and the hiccup timer expires.

### **Pre-Bias Startup**

The MxL76125 device can power up with a pre-charged output. During soft start, initially, both FETs are tri-stated. Once  $V_{REF}$  exceeds  $V_{FB}$ , the control loop takes over and switching starts to regulate the output. The MxL76125 starts in DCM to ensure that the output is not discharged. Figure 9 on page 7 shows a typical pre-bias startup waveforms.

# **Programming the Output Voltage**

The feedback reference,  $V_{REF}$  is internally fixed to 0.6V. To obtain the desired output voltage,  $(V_{OUT})$ , use a feedback divider ( $R_{FB1}$ - $R_{FB2}$ ), as shown in Figure 1 on page 1.

$$\frac{V_{REF}}{V_{OUT}} = \frac{R_{FB2}}{R_{FB1} + R_{FB2}} \Rightarrow R_{FB2} = R_{FB1} \times \frac{0.6}{V_{OUT} - 0.6}$$

(3)

MaxLinear recommends that the value of  $R_{FB1}$  is 4.99k $\Omega$ . However, you can change it as per VID resolution requirement, as described in the "VID Functionality" section.

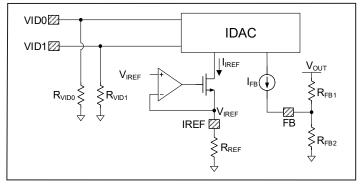

# **VID Functionality**

Nominal output voltage is set by an appropriate choice of feedback resistors, as described in the "Programming the Output Voltage" section. The output voltage can be varied from nominal in fixed step (50mV typical), by using VID0 and VID1 pins, as listed in Table 1. For more information about logic high/low voltage levels of these pins, see "Electrical Characteristics" on page 2. These pins have high input impedance and are required to be pulled to appropriate levels externally. If unused, these pins should be connected to ground or pulled down with external resistors, R<sub>VIDx</sub>.

Figure 29 shows the VID functional diagram. VID implementation includes an IDAC. The reference current  $I_{IREF}$  is set by an accurate internal reference ( $V_{IREF}$ ) and an external resistor  $R_{REF}$ . These are related as follows:

$$I_{REF} = \frac{V_{IREF}}{R_{REF}}$$

(4)

The recommended value of R<sub>REF</sub> is  $56.2k\Omega$ . I<sub>REF</sub> and VID govern current sourced by FB pin (I<sub>FB</sub>), as listed in the following table.

Table 1. VID vs  $V_{OUT}$  for VID step being 50mV (R<sub>FB1</sub> = 4.99k $\Omega$ , R<sub>REF</sub> = 56.2k $\Omega$ )

| VID1 | VID0 | VOUT            | FB Current, I <sub>FB</sub> |

|------|------|-----------------|-----------------------------|

| 0    | 1    | Nominal + 50mV  | -l <sub>IREF</sub>          |

| 0    | 0    | Nominal         | 0                           |

| 1    | 0    | Nominal - 50mV  | I <sub>IREF</sub>           |

| 1    | 1    | Nominal - 100mV | 2 x I <sub>IREF</sub>       |

${f Note:}$  + I<sub>FB</sub> implies current flowing out of the FB pin and -I<sub>FB</sub> implies current entering into the FB pin.

In steady state the feedback node voltage (V<sub>FB</sub>) is controlled to a fixed reference (V<sub>REF</sub>). As a result, when I<sub>FB</sub> flows out of the FB pin, current through R<sub>FB1</sub> is reduced by the same amount. Therefore, the voltage across R<sub>FB1</sub> is reduced by I<sub>FB</sub>×R<sub>FB1</sub>. The output voltage also decreases by the same magnitude. Hence, the VID step size,  $\Delta V_{VID}$  is expressed in terms of R<sub>FB1</sub> and I<sub>REF</sub> as follows:

$$\Delta V_{VID} = R_{FB1} \times I_{IREF} = R_{RB1} \times \frac{V_{IREF}}{R_{REF}}$$

(5)

Figure 29. MxL76125 VID Functional Diagram

# **Applications Information (Continued)**

Similarly, if  $I_{FB}$  flows into the FB pin (as listed in the fist line of Table 1 on page 12) the current through  $R_{FB1}$  is increased by the same amount as  $I_{FB}$ . Therefore, the voltage across  $R_{FB1}$  is increased by  $I_{FB} \times R_{FB1}$ . The output voltage also increases by the same magnitude.

### Wi-Fi 7 SoC Design Example

- Target nominal output voltage = 800mV.

- VID step size = 50mV.

- Feedback reference voltage = 600mV (V<sub>REF</sub>).

# From Figure 1 on page 1:

$$\frac{R_{FB2}}{R_{FB1} + R_{FB2}} = \frac{600 \text{mV}}{800 \text{mV}} \Rightarrow \frac{R_{FB2}}{R_{FB1}} = 3$$

(6)

From (5) and (6), for  $R_{REF}=56.2k\Omega,$  the recommended feedback resistors are:  $R_{FB1}=4.99k\Omega$  and  $R_{FB2}=15k\Omega.$

# **Power Good (PGOOD) Function**

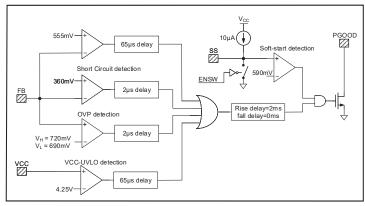

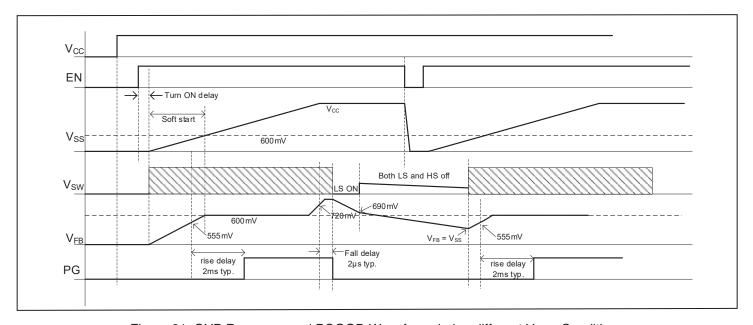

Figure 30 shows a simplified functional block diagram for the PGOOD pin. This pin is an open drain output and has active high logic. Therefore, this pin needs to be pulled up. The pull-up voltage can be tied to the VCC or some external supply. During regular operation the PGOOD is high, if the  $V_{FB} \ge 92.5\%$  of the  $V_{REF}$  (555mV). The PGOOD assertion delay is typically 2ms. The typical waveform of the PGOOD during different intervals of operation is shown in Figure 31.

Figure 30. PGOOD Function Block Diagram

Figure 31. OVP Response and PGOOD Waveform during different  $V_{OUT}$  Conditions (a) VCC = 0, (b) Soft Start, and (c) OV Fault

The PGOOD is de-asserted in any of the following events:

- During soft start.

- During output short circuit. V<sub>FB</sub> < 360mV (60% of V<sub>RFF</sub>). PGOOD de-assertion delay = 2µs.

- Output under voltage condition (369mV < V<sub>FB</sub> < 555mV). PGOOD de-assertion delay = 65µs.

- If OVP is detected (V<sub>FB</sub> ≥ 720mV). PGOOD de-assertion delay = 2µs.

- VCC < UVLO threshold (4.25V typical). PGOOD de-assertion delay = 65µs.

- If  $V_{IN} = V_{CC} = 0$  (The MxL76125 is unpowered).

- If  $T_J \ge 138^{\circ}C$  (over temperature fault).

- Over current protection is triggered.

- If the EN is low, the delay from the EN going low to PGOOD low is up to 350 ns.

The PGOOD pin is low impedance when the MxL76125 is unpowered. It ensures that the device does not give any invalid PGOOD signal if the input supply is removed.

# Operation

A typical application schematic is shown in Figure 1 on page 1. The external components that require appropriate selection for a given application are the input capacitance  $(C_{IN})$ , the output filter components  $(C_{OUT} - L_{OUT})$ , and the switching frequency (or  $T_{ON}$ ) selection resistor  $(R_{ON})$ . All other component values in the typical application schematic are recommendations for safe operation of the device.

#### Programming the On-Time (T<sub>ON</sub>)

For a given switching frequency ( $F_{SW}$ ) required value of  $T_{ON}$  is as follows:

$$T_{\rm ON} = \frac{V_{\rm OUT}}{V_{\rm IN} \times 1.06 \times F_{\rm SW} \times \eta}$$

(7)

Where  $\eta$  is the converter efficiency.

The MxL76125 allows you to set  $T_{ON}$  by using resistor  $R_{ON}$ . The corresponding relation is expressed as follows:

$$R_{ON} = V_{IN} \times \frac{T_{ON} - 2.5 \times 10^{-8}}{3.45 \times 10^{-10}}$$

(8)

Table 2 lists the values of  $R_{ON}$  for different  $V_{OUT}$  at  $V_{IN}$  = 12V,  $F_{SW}$  = 1MHz, and  $I_{OUT}$  = 15A. It uses efficiency numbers from Figure 2 on page 1.

Table 2:  $R_{ON}$  Recommendation for  $V_{IN} = 12V$

| V <sub>OUT</sub> | η%   | F <sub>sw</sub> (MHz) | R <sub>ON</sub> kΩ |

|------------------|------|-----------------------|--------------------|

| 0.8V             | 78.8 | 1                     | 1.82               |

| 3.3V             | 91.2 | 1                     | 9.31               |

Note that during soft start, the MxL76125 operates with minimum T<sub>ON</sub>, which is typically 55ns.

# Selection of the Output Filter Inductor (LOUT)

A larger inductor offers smaller switching ripple in inductor current and in  $V_{OUT}$ , but at cost of larger physical size. To balance size and ripple current magnitude, the recommended peak to peak ripple ( $\Delta I_L$ ) is 25%-40% of full load. The inductance is calculated as follows:

$$L_{OUT} = \frac{(V_{IN} - V_{OUT})}{F_{SW} \times \Delta I_{L}} \times \frac{V_{OUT}}{V_{IN}}$$

(9)

#### Example:

14

For  $V_{IN}$  = 12V,  $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 15A,  $F_{SW}$  = 1MHz and  $\Delta I_L$  = 5A, from (9)  $L_{OUT}$  = 150nH

#### Selection of the Output Capacitor (COUT)

The output filter capacitor is designed considering unloading transient overshoot, loading transient undershoot, and steady state ripple specifications, individually. The final capacitance is maximum of the three values meeting these specifications.

239DSR01

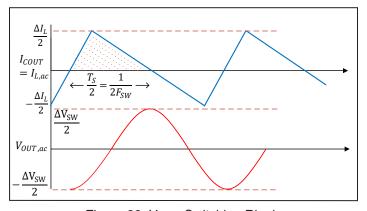

# Filter capacitor design for meeting switching ripple specifications

In this analysis, parasitic inductance and resistance of the output filter capacitor are neglected.

In steady state the inductor ripple current is filtered by  $C_{OUT}$ . The charge which produces switching ripple in  $C_{OUT}$  is the area under the shaded triangle as shown in Figure 32. Mathematically:

$$Q_{COUT} = C_{OUT} \Delta V_{SW} = \frac{1}{2} \times \frac{\Delta I_L}{4F_{SW}}$$

(10)

where, the  $\Delta V_{SW}$  is the peak to peak switching ripple in the  $V_{OUT}$ . Hence, the minimum capacitance to meet steady state  $V_{OUT}$  ripple is as follows:

$$C_{OUT_{RIPPLE}} \ge \frac{\Delta I_L}{8 \times F_{SW} \times \Delta V_{SW}}$$

(11)

Note that the regulator runs as expected when the steady state switching ripple on the FB node is below 50mV. From this an upper bound on  $\Delta V_{SW}$  for  $C_{FF} \neq 0$  is as follows.

$$\Delta V_{SW} \le 50 \text{mV}$$

(12)

Figure 32. V<sub>OUT</sub> Switching Ripple

# Filter capacitor design for meeting transient overshoot specifications

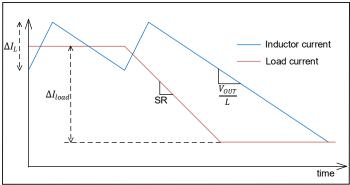

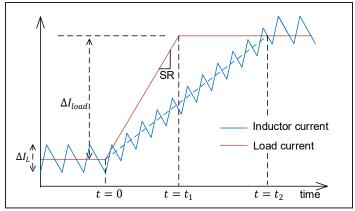

The transient overshoot happens when the load current is rapidly reduced (load throw off event). In this situation, the load slew rate (SR) magnitude is larger than the inductor current falling rate, as shown in Figure 33. In a COT controlled converter, the maximum overshoot in the output voltage can happen, when the load throw-off occurs immediately after start of a TON pulse. Accordingly, the required capacitance is as follows:

$$C_{\text{OUT\_OV}} = \frac{1}{2 \Delta V_{\text{OV}}} \times \left( \Delta I_{\text{load}} + \frac{\Delta I_{\text{L}}}{2} \right)^{2} \times \left( \frac{L}{V_{\text{OUT}}} \right) + \frac{(T_{\text{ON}} \times \Delta I_{\text{load}})}{\Delta V_{\text{OV}}} - \frac{(\Delta I_{\text{load}})^{2}}{SR \Delta V_{\text{OV}}}$$

(13)

Figure 33 Inductor Current during Unloading

Figure 34. Inductor Current during Loading

# Filter capacitor design for meeting transient undershoot specifications

The transient undershoot occurs when the load current rapidly increases. In this case, the load current slew rate is larger than the inductor current ramp up rate. In a COT controlled converter, when  $V_{\text{OUT}}$  drops, the off duration shrinks to its minimum value ( $T_{\text{OFFMIN}}$ ) and  $T_{\text{ON}}$  remains unchanged. Worst-case for transient undershoot is when the inductor current is at its valley and loading event starts. In this case, the required output filter capacitance is as follows:

$$C_{OUT\_UV} = \frac{0.5 \times (t_2 - t_1) \times \Delta I_{load} + 0.25 \times \Delta I_L \times t_2}{\Delta V_{UV}}$$

(14)

where, the load current transition time is:

$$t_1 = \frac{\Delta I_{load}}{SR} \quad (15)$$

and the inductor current transition time is:

15

$$t_{2} = \left(\frac{\Delta I_{L}}{2} + \Delta I_{load}\right) \times \frac{L}{V_{IN} \times \left(\frac{T_{ON}}{T_{ON} + T_{OFFMIN}}\right) - V_{OUT}}$$

(16)

239DSR01

### Selection of Input Capacitor (CIN)

The input current to the converter is discontinuous in nature. Input capacitors ( $C_{IN}$ ) are required to supply choppy AC currents while maintaining the DC supply voltage. For a given input voltage ripple ( $\Delta V_{IN}$ ), the required input capacitance, as a function of duty cycle ratio (D) is as follows:

$$C_{IN} \ge \frac{D \times (1 - D) \times I_{load}}{\Delta V_{IN} \times F_{SW}}$$

(17)

Net r.m.s. current in C<sub>IN</sub> is:

$$I_{\text{CIN,RMS}} = I_{\text{load}} \times \sqrt{D \times (1 - D)} \times \sqrt{1 + \frac{1 - D}{12} \left(\frac{V_{\text{OUT}}}{L \times F_{\text{SW}} \times I_{\text{OUT}}}\right)^2}$$

(18)

Considering the space constraint and depending on the application, these capacitors are typically a combination of electrolytic capacitors, ceramic capacitors (MLCC), and/or SP capacitors. Typical combinations of the PVIN capacitors are as follows:

$PV_{IN}$  = 12V,  $V_{OUT}$  = 0.8V Example: POSCap 1 x 270uF, MLCC's 2 x 22uF or 4 x 10uF, 2 x 2.2uF.

The MLCC's must have low ESR and ESL. To reduce switching spikes across the FETs, inductance in loop formed by these ceramic capacitors and FETs should be minimized.

# Feed-Forward Capacitor ( $C_{FF}$ ) and Feed-Forward Resistor ( $R_{FF}$ )

These two are connected in series and placed across  $R_{FB1}$  as shown in Figure 1 on page 1. With this, the  $V_{OUT}$  to  $V_{FB}$  open loop transfer function is as follows:

$$\frac{V_{FB}(s)}{V_{OUT}(s)} = \frac{R_{FB2}}{R_{FB1} + R_{FB2}} \times \frac{1 + (R_{FB1} + R_{FF}) C_{FF}s}{1 + \left(\frac{R_{FB1}R_{FB2}}{R_{FB1} + R_{FB2}} + R_{FF}\right) C_{FF}s}$$

(19)

It shows that,

- $C_{FF}$  introduces a low frequency zero  $(\omega_z)$  and high frequency pole  $(\omega_P)$ , which gives phase boost in a range of frequency from  $\omega_z/10$  to  $10\omega_P$ .

- With increase in R<sub>FF</sub>, the frequency of both the pole and zero reduces.

- With  $R_{FF} = 0$ , ratio of  $\omega_z$  and  $\omega_P$  (<1) is the same as the feedback attenuation ratio. With increase in  $R_{FF}$ , this ratio moves towards unity. Therefore, for low  $V_{OUT}$ , phase boosting is not helpful.

As a rule of thumb,  $C_{FF}$  should be selected such that  $\omega_z$  is 5 times of buck output filter resonance frequency, and  $R_{FF} << R_{FB1}$ . Hence,

$$C_{FF} \approx \frac{\sqrt{L_{OUT}C_{OUT}}}{5 \times R_{FB1}}$$

(20)

You must use manufacturer's DC derating curves to determine the effective capacitance corresponding to  $V_{OUT}$ . A load step test and/or a loop frequency response test should be performed. From this  $C_{FF}$  can be adjusted to get damped transient load response.

The frequency of the pole in (19) should be below the switching frequency, F<sub>SW</sub> to add gain margin. Hence,

$$R_{FF} = \frac{1}{2\pi F_{SW} C_{FF}} \qquad (21)$$

In the MxL76125, the  $C_{FF}$  also decides the  $V_{OUT}$  transition rate during DVS. The corresponding time constant,  $\tau_{DVS}$ , is as follows:

$$\tau_{\rm DVS} = R_{\rm FB1} \times C_{\rm FF} \tag{22}$$

#### Wi-Fi 7 SoC Design Example

For the parameters given in the Wi-Fi 7 SoC design example on page 13 and  $\tau_{DVS}$  = 2 $\mu$ s, from (22):

$$R_{FF} = 0$$

and  $C_{FF} = 400pF$

16 239DSR01

#### **Device Protection**

#### **Overvoltage Protection (OVP)**

The OVP detection is based on the FB pin voltage. The OVP threshold is set to 720mV, which is 1.2 times  $V_{REF}$ . When the FB voltage exceeds the OVP threshold, an internal overvoltage signal is asserted with a typical delay of 2 $\mu$ s. This signal latches off the high-side FET, turns on the low-side FET and de-asserts PGOOD. The low-side FET remains on to discharge the output capacitor until the FB voltage drops to 690mV (1.15 x  $V_{REF}$ ). Then low-side FET also turns off to prevent complete discharge of  $V_{OUT}$ . Both FETs remain latched off until the  $V_{IN}$  or EN is recycled. Note that the OVP protection is designed to protect the SoC. If a strong external source is connected to the output, the low side MOSFET can be damaged.

#### **Overcurrent Protection (OCP)**

The OCP threshold is referred to inductor valley current. If the valley current exceeds the programmed threshold, the  $I_{\rm OCP}$  for four consecutive switching cycles, the regulator enters hiccup mode. In this mode, switching is turned off for hiccup timeout period. Following the hiccup timeout, a soft start is attempted. If the OCP persists, hiccup timeout repeats. The regulator remains in hiccup mode until the load current is reduced to ensure that the valley current is below the programmed value. The OCP threshold is internally set to 20A (typical).

#### **Short-Circuit Protection (SCP)**

If the output voltage drops below 60% of its programmed value (that is, FB drops below 0.36V), the regulator enters hiccup mode. The hiccup mode persists until short-circuit is removed. Note that the SCP is activated only after PGOOD goes high. Therefore, during short circuit the SCP turns off the device the first time, but in subsequent hiccups the OCP turns off the device.

#### **Over Temperature Protection (OTP)**

The OTP is triggered when the junction temperature reaches 138°C (typical). The protection feature turns OFF both power FETs until the junction cools down to 123°C. After this, soft start is initiated and regular operation resumes.

#### **Thermal Design**

The proper thermal design is critical in controlling device temperatures and in achieving robust designs. There are several factors that affect the thermal performance, such as the temperature rise of the device in the package. This is a function of the thermal resistances of the MxL76125 inside the package and the power being dissipated.

For more information about thermal resistances, see "Electrical Characteristics" on page 2. Note that the values are obtained from simulation. Since your actual board design could be different, the thermal resistances in your actual and final board design may differ to the values listed in that section. The package thermal derating curves are shown in Figure 24 and Figure 25 on page 9.

17 239DSR01

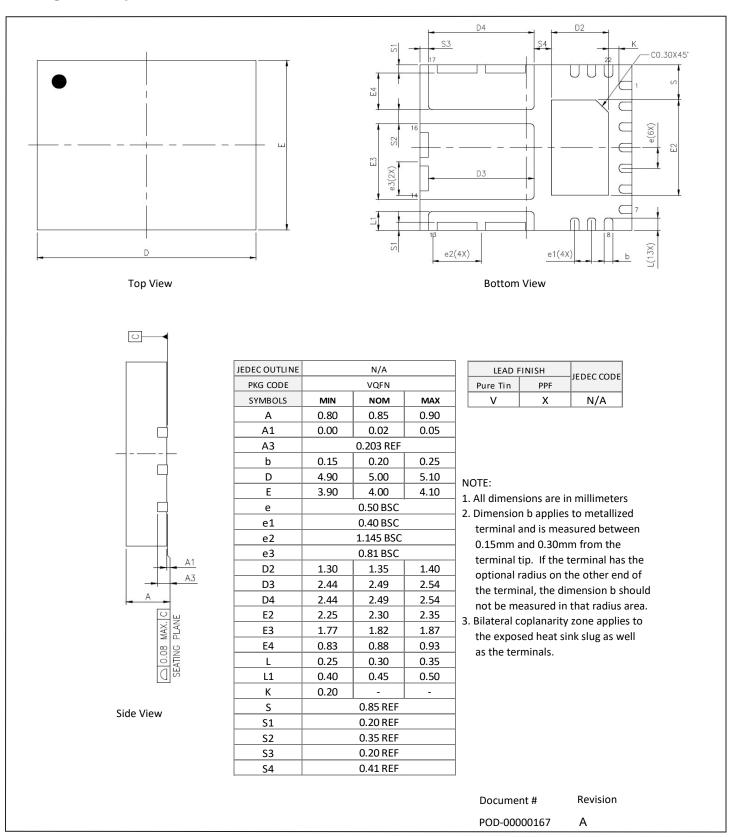

# **Package Description**

Figure 35. MxL76125 Package Description

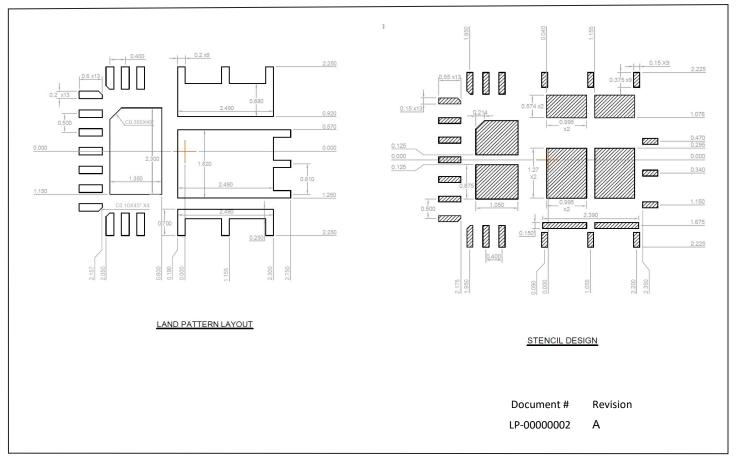

# **Land Pattern and Stencil Design**

Figure 36. MxL76125 Land Pattern and Stencil Design

# **Ordering Information**

| Part Number    | Operating Temperature Range        | Lead-Free | Package         | Packaging<br>Method |  |

|----------------|------------------------------------|-----------|-----------------|---------------------|--|

| MxL76125-AQB-R | -40°C ≤ T <sub>J</sub> ≤ 125°C Yes |           | 4mm x 5mm (QFN) | Tape and Reel       |  |

| MxL76125-EVK-1 | MxL76125 Evaluation Board.         |           |                 |                     |  |

**Note:** For more information about part numbers, as well as the most up-to-date ordering information and additional information on environment rating, go to <a href="https://www.maxlinear.com/MxL76125">www.maxlinear.com/MxL76125</a>.

# **Revision History**

| Revision | Date              | Description            |

|----------|-------------------|------------------------|

| 239DSR01 | December 20, 2022 | Initial final release. |

Corporate Headquarters: 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc.. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

© 2022 MaxLinear, Inc. All rights reserved